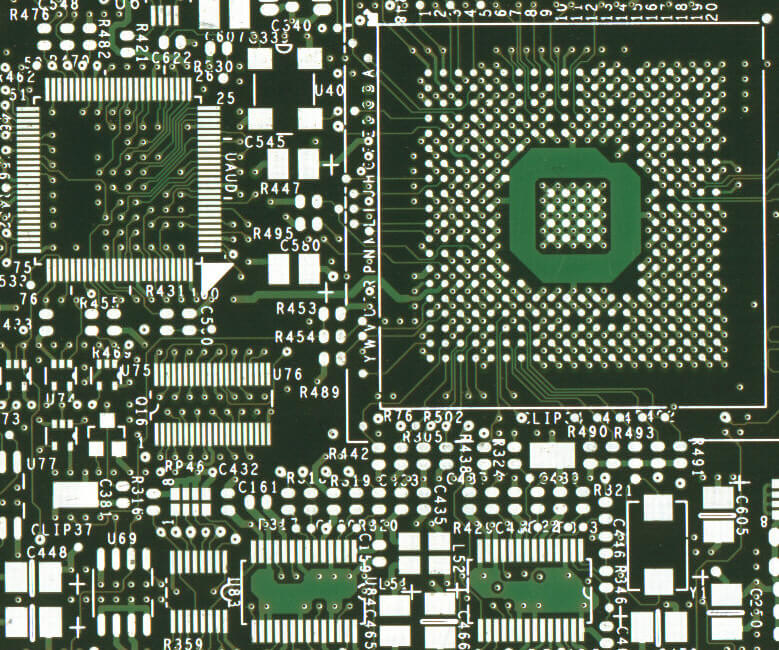

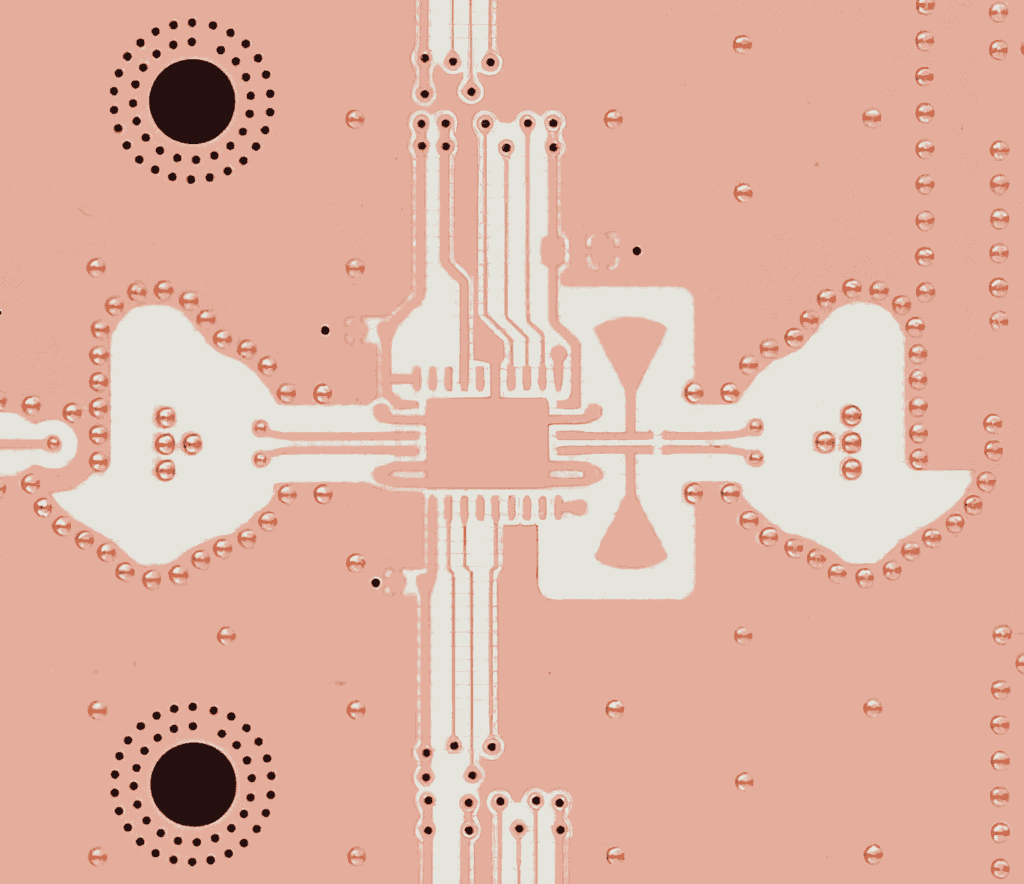

Vielfalt an Leiterplatten-Oberflächen

Leiterplattenoberflächen müssen vielfältigen Anforderungen standhalten, etwa beim Löten, Bonden, Einpressen, Kleben, o.Ä..

ANDUS ELECTRONIC bietet dafür chemische und galvanische Oberflächen: Gold, Zinn, Silber und Kupfer zählen zur breiten Auswahl. Hier wird in verschiedene Varianten unterteilt, wobei jede Oberfläche Ihre eigenen Vorteile hat. Weitere Optionen sind Carbonlack sowie selektive und kombinierte Oberflächen. Im Folgendem wird eine detaillierte Übersicht über unser Portfolio vorgestellt.

Übersicht über alle Leiterplatten-Oberflächen

Die Leiterplattenoberfläche (Endoberfläche, Metallisierung, Finish) hat die Aufgabe, das Kupfer der Anschlussflächen vor Oxidation zu schützen und für einen ausreichenden Zeitraum haltbar zu machen, um die vorgesehene Aufbau- und Verbindungstechnik (AVT) zuverlässig ausführen zu können.

Die Verbindungstechniken gehen heute weit über das Löten hinaus. Neben der Lötbarkeit der Oberflächen müssen oft weitere Anforderungen erfüllt werden.

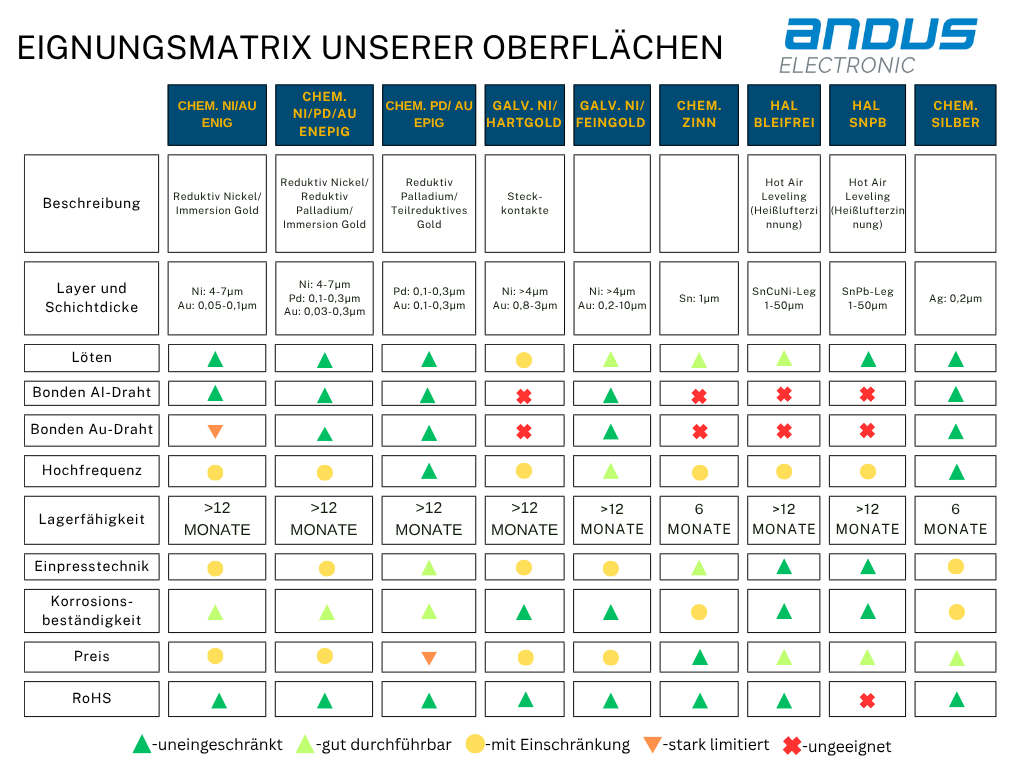

Unter unserer Eignungsmatrix können Sie eine kompakte Übersicht von allen Oberflächen in unserem Portfolio bekommen und alle wichtigen Informationen zu ihrer Funktion:

- Löten, oft mehrfach bei Temperaturen für bleifreies Lot. In Ausnahmen Löten mit Zinn-Blei-Loten oder mit Hochtemperaturloten

- Bonden mit AIuminium-Draht

- Bonden mit Gold-Draht

- Hochfrequenztauglichkeit (Skin-Effekt)

- Lagerfähigkeit

- Tastaturkontakte

- Korrosionsbeständigkeit

- Einpresstechnik

- Preis

Goldoberflächen

Chemisch Nickel Gold – ENIG

Die Oberfläche chem. Ni/Au = Electroless Nickel(-Phosphor)/Immersion Gold = ENIG = Sudgold = Flash-Gold ist die am häufigsten verwendete Oberfläche. Sie ist sowohl für das Aluminiumdraht-Bonden als auch für das Mehrfach-Löten gut geeignet und somit die ideale Oberfläche für die Kombination beider Verbindungstechniken. Sie besteht aus einer 4-6 µm dicken Nickelschicht, die prozesstechnisch bedingt üblicherweise 6-8 % Phosphor enthält. Als Anlaufschutz ist die Nickelschicht mit 70 nm – 120 nm Gold beschichtet. Die Lagerzeit beträgt mehr als 12 Monate.

Die Goldschicht löst sich beim Löten komplett im Zinn auf. Die eigentliche Lötverbindung kommt dann mit einer intermetallischen Ni/Sn-Phase zwischen dem Lot und er Nickelschicht zustande.

Chemisch Nickel/Palladium/Gold – ENEPIG

Für das Golddrahtbonden wird zwischen Nickel und Gold eine Palladiumschicht abgeschieden. Das gewährleistet eine gute Haftung des Gold-Bonddrahts. Ansonsten weist die ENEPIG Oberfläche die gleichen Eigenschaften wie ENIG auf. ENEPIG lässt sich genauso löten wie ENIG. Galvanische Feingold-Schichten werden zwar auch per Golddraht gebondet, lassen sich jedoch aufgrund des höheren Goldanteils in der Lötstelle nicht immer zuverlässig löten.

Damit ist ENEPIG eine universelle Oberfläche für alle Bond- und Lötverfahren.

Galvanisch Gold Oberflächen

Galvanisch Nickel/Gold (Feingold)

Alternativ zum ENEPIG kann die Oberfläche für das Goldraht-Bonden galvanisch aufgebracht werden. Beim Löten hingegen löst sich das Gold im Zinn. Bei kleinen Lotmengen kann der Goldanteil im Zinn so hoch werden, dass sich spröde Zinn-Gold-Phasen ausbilden, die die Lötstelle schwächen.

Die Lagerzeit beträgt mehr als 12 Monate.

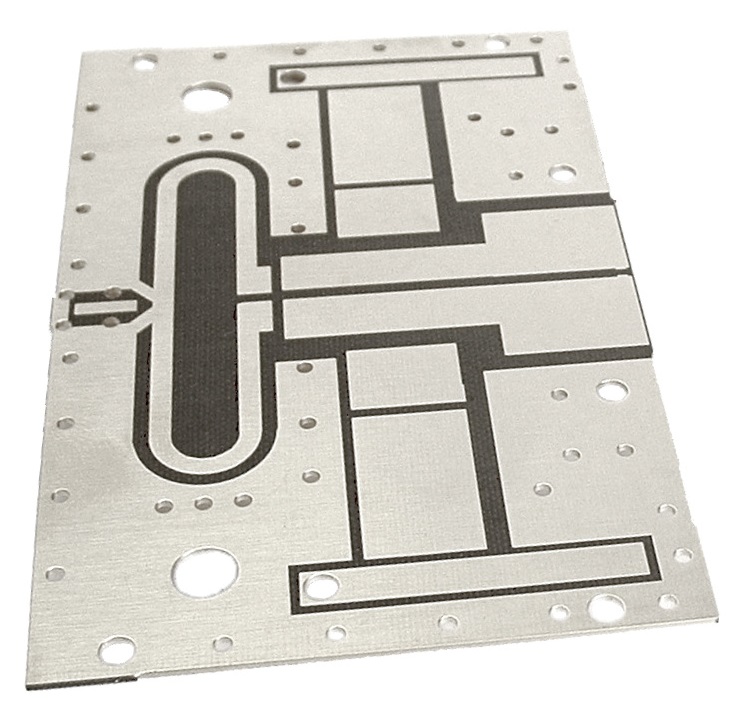

Galvanisch Nickel/Hartgold (Steckergold)

Hartgold, welches mit Cobalt oder Nickel legiert ist (Härte 60-180 HV), wird für Einschubstecker (0,8 – 2 µm Gold), Schleifkontakten (2 – 5 µm Gold) und für langzeitstabile Tippkontakte verwendet. Auch diese Oberfläche ist nicht für das Löten vorgesehen.

Falls doch gelötet werden soll, kann galvanisches Gold an der Lötstelle durch mehrfaches Verzinnen und Entzinnen mit frischem Lot versehen werden.

Chemisch Palladium / Immersionsgold – EPIG

Die Oberfläche EPIG (Electroless Palladium / Immesion Gold) ist eine Weiterentwicklung der ENIG Oberfläche, bei der das Nickel durch dünnes Palladium ersetzt wird. Das Palladium übernimmt die Funktion des Nickels als Diffusionssperre zwischen Kupfer und Gold, die verhindert, dass im Laufe der Zeit Gold ins Kupfer eindringt und Kupfer an die Oberfläche wandert.

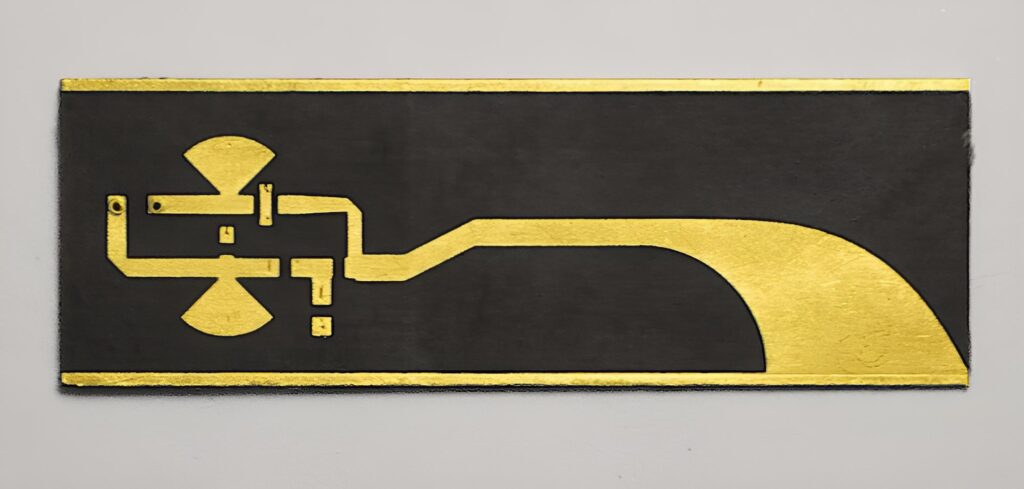

Besonders bei Hochfrequenz-Anwendungen ist EPIG interessant: Je höher die übertragenen Frequenzen, desto höher ist die Stromdichte an der Oberfläche der Leiter. Wenn die Leiter nicht vernickelt sind, wird verhindert, dass der Strom nicht zu einem Teil durch das schlechter leitfähige Kupfer fließt, sondern weiterhin durch das gut leitfähige Kupfer.

Nickel wird manchmal auch aufgrund seiner magnetischen Eigenschaften gemieden, oder aus toxikologischen Gründen.

Direktes Immersionsgold – DIG

Bei der Oberfläche DIG (Direct Immersion Gold) wird Gold direkt auf Kupfer abgeschieden. Löten und sogar Golddraht-Bonden sind sehr gut möglich.

Eine Diffussionsbarriere wie Nickel oder Palladium existiert nicht. Daher ist Kupfer mit dieser Oberfläche gut biegbar. Die Oberfläche wird vor allem im Bereich Medizintechnik, Luft- und Raumfahrt eingesetzt, vor allem, wenn die Oberfläche auf sehr feine Strukturen aufgetragen wird.

Zinn- Oberflächen

Chemisch Zinn

Ein chemisch aufgebrachtes Zinn bildet eine 1 µm dünne, von einer Oxidschicht geschützte Oberfläche, die eine perfekte Kupfer-Zinn-Lötverbindung ohne Nickel-Zwischenschicht ermöglicht. Aufgrund der natürlichen Diffusion zwischen Zinn und Kupfer (Cu + Sn → Cu₆Sn₅ → Cu₃Sn) ist die Haltbarkeit begrenzt, da das Kupfer im Laufe der Zeit bis zur Oberfläche durchwächst.

Die empfohlene Lagerdauer beträgt maximal sechs Monate. Alle Lötprozesse sollten idealerweise innerhalb von 24 Stunden nach der Bestückung abgeschlossen sein.

HAL- Hot Air Leveling (Heißluftverzinnung)

Bei der HAL-Oberfläche (auch HASL = Hot Air Solder Leveling) wird die Leiterplatte in flüssiges SnCuNi getaucht und anschließend herausgezogen und mit Heißluft abgeblasen. Dadurch entsteht eine dicke, aber etwas ungleichmäßige Lotschicht. Für kleine SMD-Bauteile ist diese Oberfläche weniger geeignet, da der Lotpastendruck und die Positionierung auf den gewölbten Pad-Oberflächen ungleichmäßig ist. Vorteilhaft ist jedoch die perfekte Benetzung: die Pads sind bereits vollständig mit Lot bedeckt.

Neben der bleifreien Heizverzinnung mit SnCuNi existiert noch die bleihaltige SnPb-Legierung mit ca. 37% Blei. Die Schmelztemperatur liegt mit 179°C um fast 40°C unter dem bleifreien Lotbad. Dadurch ist der thermische Stress auf die Leiterplatte deutlich geringer. Aufgrund des Bleiverbots im Zuge des RoHS-Direktive von 2006 ist das Inverkehrbringen nur auf wenige Ausnahmen zulässig. Dazu zählen aktuell reine F&E-Prototypen, medizinische Implantate, Raumfahrt und ähnlich hochzuverlässige Anwendungen.

Silber & Kupfer-Oberfläche

Chemisch Silber

Chemisch Silber (Immersion Ag) ist eine Oberfläche für Leiterplatten, die besonders bei Hochfrequenzanwendungen zum Einsatz kommt. Sie bietet bei hohen Frequenzen sehr gute elektrische Eigenschaften, geringe Leitungsverluste und eignet sich ideal für präzise Schaltungen, etwa in der Telekommunikation oder Medizintechnik.

Die silberne Schicht wird direkt auf das Kupfer aufgebracht, ist gut lötbar und für mehrfaches Löten geeignet, ist jedoch nicht bondbar. Sollte es mehrfach gelötet werden, sind keine längeren Liegezeiten zulässig.

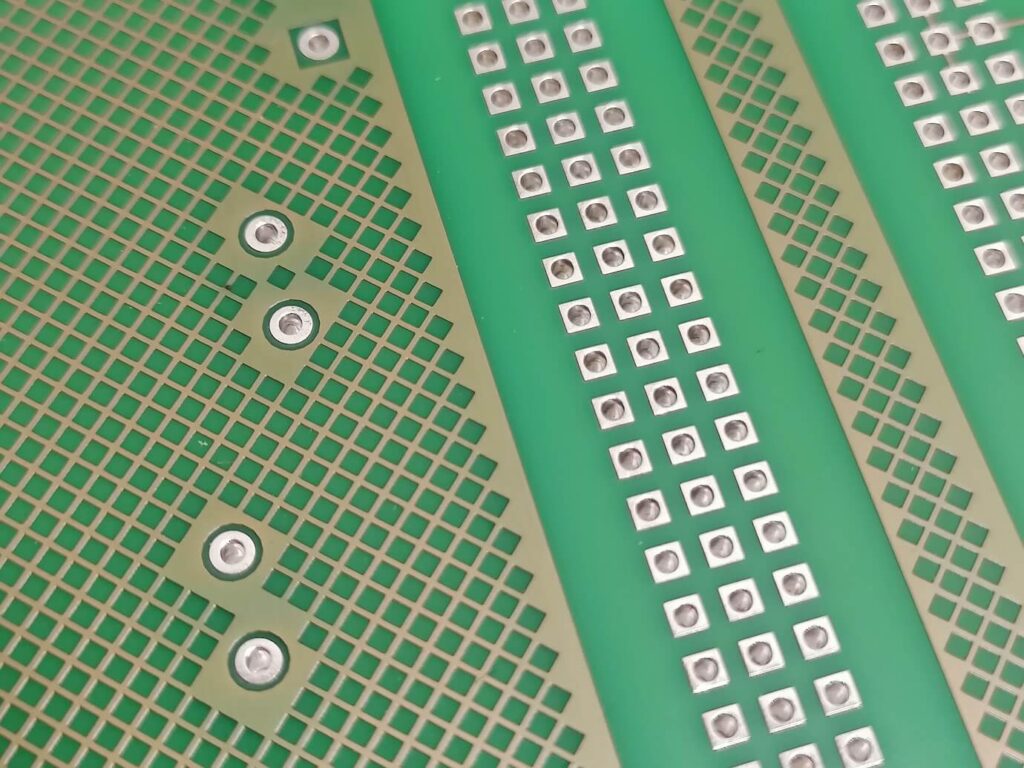

Kupfer mit organischer Schutzbeschichtung (OSP)

OSP ist eine kostengünstige Kupferoberfläche mit organischer Schutzbeschichtung. Diese schützt das Kupfer bis zum ersten Lötprozess, bei dem die Schicht aufbricht. Mehrfaches Löten ist daher eher die Ausnahme, da die Schutzwirkung nach dem ersten Durchgang verloren geht.

Spezielle und seltene Leiterplattenoberflächen

Oberflächen Raritäten

Neben den gängigen Oberflächen finden in bestimmten Anwendungen auch seltenere Varianten Einsatz. Fused SnPb beschreibt galvanisch abgeschiedenes Zinn-Blei, das nachträglich aufgeschmolzen wird. Diese Oberfläche ist insbesondere im Space-Bereich gefordert. Ersatzweise wird heute HAL SnPb als bleihaltige Variante des Hot-Air-Levelings aufgebracht. Beide Oberflächen sind nicht RoHS-konform und dürfen nur in zulässigen Ausnahmen verwendet werden.

Eine weitere Sonderoberfläche ist Carbonlack, der meist als Kontaktfläche in Tastaturen und Schaltern genutzt wird.

Auch galvanisch Silber (Ag) und galvanisch Zinn (Sn) finden in Einzelfällen Anwendung, wenn spezifische elektrische oder mechanische Anforderungen erfüllt werden müssen.

Lassen Sie sich kostenlos beraten!

Wir helfen Ihnen gerne weiter:

Dr. Christoph Lehnberger

Leiter Technologie